سعر فوب

أحصل على آخر سعر|

100 Piece Minimum Order

بلد:

China

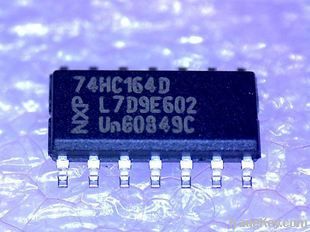

نموذج رقم:

74HC164D

سعر فوب:

الموقع:

China

سعر الحد الأدنى للطلب:

-

الحد الأدني للطلب:

100 Piece

تفاصيل التغليف:

-

موعد التسليم:

-

القدرة على التوريد:

-

نوع الدفع:

T/T

مجموعة المنتج :

-

الشخص الذي يمكن الاتصال به Mr. songhao

RM3022, Nan Guang Jie Jia Building, 3037 Shennan Road, Futian District, Shenzhen, Guangdong

The *4HC**4; *4HCT**4 are high-speed Si-gate CMOS devices and are pin compatible

with Low power Schottky TTL (LSTTL). They are speciï¬ed in compliance with JEDEC

standard no. 7A.

The *4HC**4; *4HCT**4 are *-bit edge-triggered shift registers with serial data entry

and an output from each of the eight stages. Data is entered serially through one of two

s (DSA or DSB); either can be used as an active HIGH enable for data entry

through the other . Both s must be connected together or an unused must

be tied HIGH.

Data shifts one place to the right on each LOW-to-HIGH transition of the clock (CP)

and enters into Q0, which is the logical AND of the two data s (DSA and DSB) that

existed one set-up time prior to the rising clock edge.

A LOW level on the master reset (MR) overrides all other s and clears the

register asynchronously, forcing all outputs LOW.

Gated serial data s

Asynchronous master reset

Complies with JEDEC standard no. 7A

ESD protection:

HBM EIA/JESD**-A***-B exceeds ***0 V

MM EIA/JESD**-A***-A exceeds **0 V.

Multiple package options

Speciï¬ed from −*0 °C to **5 °C and −*0 °C to ***5 °C.

| بلد: | China |

| نموذج رقم: | 74HC164D |

| سعر فوب: | أحصل على آخر سعر |

| الموقع: | China |

| سعر الحد الأدنى للطلب: | - |

| الحد الأدني للطلب: | 100 Piece |

| تفاصيل التغليف: | - |

| موعد التسليم: | - |

| القدرة على التوريد: | - |

| نوع الدفع: | T/T |

| مجموعة المنتج : | - |